This article was downloaded by: [University of Haifa Library]

On: 16 August 2012, At: 12:47 Publisher: Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH,

UK

# Molecular Crystals and Liquid Crystals Science and Technology. Section A. Molecular Crystals and Liquid Crystals

Publication details, including instructions for authors and subscription information: <a href="http://www.tandfonline.com/loi/gmcl19">http://www.tandfonline.com/loi/gmcl19</a>

# Electrical Characteristics of Pentacene Organic Thin Film Transistors with Silicon Dioxide Gate Insulator

Jong Sun Choi  $^{\rm a}$  , Dae-Yop Kim  $^{\rm a}$  , Jae-Hyuk Lee  $^{\rm a}$  , Dou-Yol Kang  $^{\rm a}$  , Young-Kwan Kim  $^{\rm b}$  & Dong-Myung Shin  $^{\rm c}$

Version of record first published: 24 Sep 2006

To cite this article: Jong Sun Choi, Dae-Yop Kim, Jae-Hyuk Lee, Dou-Yol Kang, Young-Kwan Kim & Dong-Myung Shin (2000): Electrical Characteristics of Pentacene Organic Thin Film Transistors with Silicon Dioxide Gate Insulator, Molecular Crystals and Liquid Crystals Science and Technology. Section A. Molecular Crystals and Liquid Crystals, 349:1, 339-342

To link to this article: <a href="http://dx.doi.org/10.1080/10587250008024933">http://dx.doi.org/10.1080/10587250008024933</a>

<sup>&</sup>lt;sup>a</sup> Department of Electrical and Control Engineering, Hong-Ik University, Seoul, Korea

<sup>&</sup>lt;sup>b</sup> Department of Applied Science, Hong-Ik University, Seoul, Korea

<sup>&</sup>lt;sup>c</sup> Department of Chemical Engineering, Hong-Ik University, Seoul, Korea

# PLEASE SCROLL DOWN FOR ARTICLE

Full terms and conditions of use: <a href="http://www.tandfonline.com/page/terms-and-conditions">http://www.tandfonline.com/page/terms-and-conditions</a>

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden.

The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae, and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand, or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material.

# Electrical Characteristics of Pentacene Organic Thin Film Transistors with Silicon Dioxide Gate Insulator

JONG SUN CHOI<sup>a</sup>, DAE-YOP KIM<sup>a</sup>, JAE-HYUK LEE<sup>a</sup>, DOU-YOL KANG<sup>a</sup>, YOUNG-KWAN KIM<sup>b</sup> and DONG-MYUNG SHIN<sup>c</sup>

<sup>a</sup>Department of Electrical and Control Engineering, Hong-Ik University, Seoul, Korea, <sup>b</sup>Department of Applied Science, Hong-Ik University, Seoul, Korea and <sup>c</sup>Department of Chemical Engineering, Hong-Ik University, Seoul, Korea

Pentacene thin-film transistors(TFTs) were fabricated on glass substrates. Aluminum and gold were used for gate and source/drain electrodes. Silicon dioxide was deposited as a gate insulator by PECVD and patterned by reactive ion etching(RIE). The semiconducting pentacene layer was thermally evaporated in vacuum at a pressure of about  $10^{-8}$  Torr and a deposition rate of 0.3 Å/sec. The fabricated devices exhibited the field-effect mobility as large as 0.07 cm<sup>2</sup>/V· sec, threshold voltage as low as -3.3V, and the on/off current ratio larger than  $10^{7}$ .

Keywords: Organic thin film transistors; pentacene; evaporation; field-effect mobility; threshold voltage; on-off current ratio

### INTRODUCTION

Some organic materials have received considerable attention as materials for the active device applications such as light emitting diodes<sup>1</sup> and TFTs<sup>2</sup>. They

can offer potential advantages in terms of the processing simplicity and manufacturing cost<sup>3</sup>. In this study, pentacene TFTs were fabricated on glass substrates. Aluminum and gold were used for the gate and source/drain electrodes respectively. Silicon dioxide was deposited for the gate insulator by plasma enhancement chemical vapor deposition(PECVD) and etched by RIE for patterning. The operational properties of the fabricated TFTs were characterized by the field-effect mobility, threshold voltage and on/off current ratio.

#### DEVICES FABRICATION

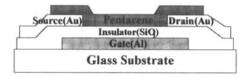

The schematic cross-section of a pentacene TFT is shown in Figure 1. Aluminum was deposited on the glass substrate by the conventional thermal evaporation, patterned by the lift-off, and annealed. The gate insulator, SiO<sub>2</sub> was deposited by PECVD. The SiO<sub>2</sub> layer was patterned by R.I.E., the thickness of which was about 100 nm. Then, gold was deposited on the gate insulator by the thermal evaporation, whose thickness was 130 nm.

Figure 1. The schematic cross-section of the pentacene TFT fabricated in this study.

# RESULT AND DISCUSSION

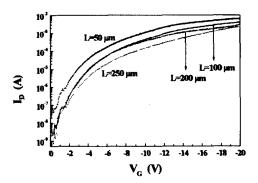

The transfer characteristics of pentacene TFTs, whose channel lengths are 50, 100, 200, and  $250\mu$ m respectively, are presented in Figure 2. The channel width of all the devices is 5 mm. The drain bias was 2 V and the gate bias varied from 0V to -20V for the measurements. The on/off current ratio of those devices is larger than  $10^7$ , which is one of the best data. The mobility and threshold voltage were extracted from the  $I_D$  vs.  $V_G$  data measured in the saturation regime, based on the equation<sup>4</sup>:

$$I_{DS} = \frac{WC_i}{L^2} \mu (V_G - V_{Ih})^2$$

Figure 2. Transfer characteristics of pentacene TFT with gate lengths of 50, 100, 200, 250  $\mu$ m, width of 5 mm ( $V_D = 2V$ )

where  $\mu$  is the field-effect mobility, L and W are the channel length and width, respectively,  $C_i$  is the gate capacitance per unit area, and  $V_{th}$  is the threshold voltage.  $V_{th}$  and  $\mu$  were extracted from the plot of  $I_D^{1/2}$  vs.  $V_G$  measured in the saturation regime. The field-effect mobility is as large as 0.07 cm²/V· sec, which is remarkably high if it is taken account of that the pentacene layer was deposited by the plain thermal. Moreover,  $V_{th}$  is as low as -3.30 V, which is one of the lowest turn-on voltages ever reported. The excellent characteristics of the fabricated TFTs are thought to be

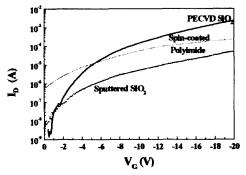

Figure 3. Transfer characteristics of pentacene TFTs with various gate insulators. (L=  $50\mu m$ , W= 5 mm at  $V_D = 2V$ )

attributed to the plasma treatment of the SiO<sub>2</sub> surface during the plasma etching. If an effusion cell is used under lower pressure and the substrate temperature is raised higher, the much better-ordered pentacene layer could be obtained to provide the much improved transistor characteristics that can be comparable to those of amorphous silicon TFTs.

All-organic TFTs can be realized if the SiO<sub>2</sub> is replaced by an organic dielectric medium as a gate insulator with conducting organic electrodes. The spin-coated polyimide layer was used as a gate insulator to build transistors, whose transfer characteristics is presented in Figure 3. Also is provided the transfer characteristics of a pentacene TFT with the gate insulator of sputtered SiO<sub>2</sub>. Both TFTs with the polyimide and sputtered SiO<sub>2</sub> exhibited the worse operational properties, which seem to be leaky and incomplete in the channel formation.

#### CONCULSION

Pentacene TFTs was fabricated on the glass substrate. Aluminum and gold were used for the gate and source/drain electrodes. The SiO<sub>2</sub> was deposited by PECVD and patterned by R.I.E. as a gate insulator. The pentacene layer was thermally evaporated. Electrical characterizations of the TFTs show that the field-effect mobility is as large as 0.07 cm<sup>2</sup>/V· sec, on/off current ratio over 10<sup>7</sup>, and threshold voltage as low as -3.30 V. If an effusion cell is used under lower pressure and the substrate temperature is raised higher, the much improved transistor characteristics could be obtained.

#### Acknowledgements

This study is supported by the academic research fund of ministry of education, Republic of Korea.

### References

- G. Gu and S. R. Forrest, IEEE J. Select. Topics Quantum Electron., vol. 4, pp 83-99, Jan./Feb. 1998.

- [2] X. C. Li, H. Sirringhaus, F. Garnier, A. B. Holmes, S. C. Maratti, N. Feeder, W. Clegg, S. J. Teat, J. Amer. Chem., vol. 120, P.2207, 1998.

- [3] Y. Y. Lin, D. J. Gundlach, S. F. Nelson, and T. N. Jackson, *IEEE Electron Device Lett.*, vol. 18, pp. 606–608, Dec. 1997.

- [4] A. Dodabalapur, Z. Bao, A. Makhija, J. G. Laquindanum, V. R. Raju, Y. Feng, H. E. Katz, and J. Rogers, Appl. Phys. Lett., vol. 73, pp. 142-144, 1998.